#### **Final Exam General Information**

The first page of the exam will include a detailed list of instructions and policies. You should especially note the following:

- 1. You will be allowed to use a non-wireless enabled calculator, such as a TI-99.

- 2. You will be allowed to use up to four 8.5 × 11-inch two-sided handwritten help sheets. No photocopied material or copied and pasted text or images are allowed. If there is a table or image from the textbook or some other source that you feel would be helpful during the exam, please notify me.

- 3. All help sheets will be collected at the end of the exam but will be returned to you upon request.

- 4. If you begin the exam after the start time, you must complete it in the remaining allotted time. However, you may not take the exam if you arrive after the first student has completed it and left the room. The latter case is equivalent to missing the exam.

- 5. You may not leave the exam room without prior permission except in an emergency or for an urgent medical condition. Please use the restroom before the exam.

Rough breakdown of topic coverage (two topics possibly combined into one problem):

| 1–2 problems | Small-signal modeling of NMOS/PMOS amplifiers (CS, source       |

|--------------|-----------------------------------------------------------------|

|              | follower, and CG)                                               |

| 1–2 problems | NMOS and/or PMOS channel-length modulation $(r_o)$              |

| 1–2 problems | PMOS regions of operation and bias design                       |

| 1–2 problems | CMOS logic gate circuits                                        |

| 1 problem    | Basic BJT circuit analysis (DC/bias only or switching circuits) |

The final exam is not cumulative in the sense that there will be no problems whose solutions relate specifically to the material covered before Exam #3. However, much of the material that was covered since then builds on the earlier material. (For example, you should know at a basic level how *pn*-junctions work, you should be able to determine the region of operation of a MOSFET, and circuit might include a diode or two.) You must have a solid grasp of the foundational concepts that are relevant to the material that was covered after Exam #3.

The final exam will take place 8:00–10:50 am on Thursday, December 11 in Breakiron 165. The exam will be designed to be completed in just over one hour, but you may use the full three hours. You must begin the exam at or soon after 8:00 am. You will not be allowed to take the exam if you arrive after the first student has completed it and left the room.

The final exam score, like the in-semester exam scores, will be eligible for reduced weighting when the overall average score for the semester is calculated. If your final exam score is lower than your three in-semester exam scores, then it will be weighted only 5% instead of 20%.

Solutions to the final exam will not be posted, but you may review your final exam and discuss it with me at any time after it has been graded, even next year. Your final exam score will be posted at the course Moodle site.

## **Review Topics for ECEG 350 Final Exam**

The following is a list of topics that could appear in one form or another on the exam. Not all of these topics will be covered, and it is possible that an exam problem could cover a detail not specifically listed here. However, this list has been made as comprehensive as possible. You should be familiar with the topics on the previous review sheets in addition to those listed below.

Although significant effort has been made to ensure that there are no errors in this review sheet, some might nevertheless appear. The textbook is the final authority in all factual matters, unless errors have been specifically identified there. You are ultimately responsible for obtaining accurate information when preparing for your exam.

## DC blocking capacitors

- act as open circuits at DC (after transient phase when DC steady state applies)

- act as short circuits (or very low impedances or reactances) at signal frequencies

- isolate DC biasing from signal source and/or load

- impedance and reactance

$$Z_C = \frac{1}{j\omega C} = \frac{1}{j2\pi fC} = -j\frac{1}{2\pi fC}$$

and  $X_C = -\frac{1}{\omega C} = -\frac{1}{2\pi fC}$   $(Z_C = jX_C)$

### AC bypass capacitors

- act as open circuits at DC

- act as short circuits (or very low impedances or reactances) at signal frequencies

- ensure bypassed nodes are close to ground potential at signal frequencies

- commonly connected between power supply nodes and ground and across source degeneration resistors (FETs) or emitter degeneration resistors (BJTs)

# Amplifier nomenclature

- common-source (CS) amplifier is the basic MOSFET inverting amplifier

- common-drain (CD) amplifier is noninverting with a voltage gain close to or less than one; usually called a *source follower*

- common-gate (CG) amp is noninverting and has voltage gain comparable to CS amp, but its input resistance is much lower (comparable to output resistance of source follower)

- "common" refers to terminal connected either directly to ground or indirectly to ground through a low-impedance capacitor. One terminal of the signal source and the load have the common terminal in common.

- CS amps, CG amps, and source followers can be biased in multiple ways (e.g., 4-R network, drain-to-gate feedback resistor, current mirror); the biasing network does not determine the amplifier's nomenclature.

### General small-signal modeling of MOSFET circuits

- definition of "incremental signal" or "small signal" (fluctuations are a small fraction of total voltage or current)

- conventions used with variables that represent voltages and currents

- $\circ$  total voltage/current: lower-case variable, upper-case subscript (e.g.,  $v_{GS}$ )

- o bias (quiescent): upper-case variable, upper-case subscript (e.g.,  $V_{GS}$ )

- o signal (time-varying) and small-signal model parameters: lower-case variable, lower-case subscript (e.g.,  $v_{gs}$ ,  $g_m$ ,  $r_o$ )

- o some special constants/parameters: upper-case variable, lower-case subscript (e.g.,  $V_t$ )

- small-signal condition for MOSFETs:  $|v_{gs}| \ll 2(V_{GS} V_t)$

- separation of bias considerations (quiescent levels; output voltage swing range) from small-signal considerations (gain, input and output resistance)

- for small-signal analysis using superposition, draw small-signal representation of circuit:

- o replace transistors with their appropriate hybrid-pi models

- o replace DC voltage sources with shorts (because voltage across a DC voltage source can't change; alternative reason: a 0 V source is a signal short)

- o replace DC current sources with opens (because current through a DC current source can't change; alternative reason: a 0 A source is a signal open)

- o replace large capacitors with shorts (if capacitive reactance is insignificant at operating frequency)

- o replace small capacitors/capacitances with opens (if capacitive reactance is enormous at operating frequency)

- o replace large inductors with opens (if inductive reactance is very large at operating frequency)

- replace small inductors/inductances with shorts (if inductive reactance is insignificant at operating frequency)

- DC voltage sources are typically bypassed at AC (i.e., at signal frequencies) using large capacitors to ensure that the DC source acts as an AC ground.

- small-signal model of MOSFET a.k.a. the hybrid-pi model (only valid in sat. region)

- o voltage-controlled current source  $g_m v_{gs}$

- $\circ$  output resistance  $r_o$  due to channel-length modulation

- o gap (open) b/w gate and source

- o hybrid-pi model is the same for NMOS and PMOS devices

- small-signal model of drain-to-source path represented by  $r_{DS}$  is only valid when MOSFET operates in the low- $v_{DS}$  triode (resistive) region; i.e.,  $v_{DS} \ll v_{GS} V_t$

- small-signal model of MOSFET in cut-off region consists of open circuits between all terminals (gate, source, drain)

- derivation of small-signal voltage gain  $v_o/v_{in}$  (or "overall gain"  $v_o/v_{sig}$  sometimes)

- simplifications can sometimes be made in gain expressions when one term is much greater/smaller than another term

- small-signal transconductance  $g_m$  (for NMOS devices; similar for PMOS)

o basic definition:

$$g_m = \frac{\partial i_D}{\partial v_{GS}}\Big|_{v_{GS} = V_{GS}}$$

; can be derived from

$$I_D + i_d = \frac{1}{2}k_n(V_{GS} + v_{gs} - V_t)^2 = \frac{1}{2}k_n(V_{GS} - V_t)^2 + k_n(V_{GS} - V_t)v_{gs} + \frac{1}{2}k_nv_{gs}^2$$

$$\approx \frac{1}{2}k_n(V_{GS} - V_t)^2 + k_n(V_{GS} - V_t)v_{gs}$$

$$\rightarrow i_d = k_n (V_{GS} - V_t) v_{gs} = g_m v_{gs}$$

and  $I_D = \frac{1}{2} k_n (V_{GS} - V_t)^2$ ,

where  $|v_{gs}| \ll 2(V_{GS} - V_t)$  and  $g_m = k_n(V_{GS} - V_t)$

o equivalent formulas (these are for NMOS devices; similar formulas for PMOS):

$$g_m = k_n V_{OV} = k_n (V_{GS} - V_t) = \frac{2I_D}{V_{GS} - V_t} = \sqrt{2k_n I_D}$$

, where  $k_n = k_n' \frac{W}{L} = \mu_n C_{ox} \frac{W}{L}$

Finite output (drain-to-source) resistance  $r_o$  of MOSFETs (channel-length modulation)

- represents slope of  $i_D$ - $v_{DS}$  characteristic in the saturation region due to channel-length modulation (sometimes referred to as the Early effect, although that term technically applies only to BJTs)

- channel-length modulation parameter:  $\lambda = \frac{1}{V_A + V_{OV}} \approx \frac{1}{V_A}$ ,

where  $V_A$  = Early voltage

- $r_o \approx \frac{V_A}{I_D} \approx \frac{1}{\lambda I_D}$ , where  $I_D$  is the quiescent drain current

- $r_o$  is typically 20–100 k $\Omega$  for MOSFETs but can be lower for some types, especially integrated MOSFETs; it can be a major factor limiting amplifier gain

- $r_o$  is <u>not</u> equal to  $r_{DS}$  of MOSFET in low- $v_{DS}$  triode region!  $r_o$  is only relevant in the saturation region

- *i-v* characteristic in saturation region that includes  $\lambda$ :

$$i_D = \frac{1}{2} k_n v_{OV}^2 \left[ 1 + \lambda \left( v_{DS} - v_{OV} \right) \right] \approx \frac{1}{2} k_n v_{OV}^2 \left( 1 + \lambda v_{DS} \right), \text{ where } v_{OV} = v_{GS} - V_t$$

#### Source follower circuits

- less commonly called a *common-drain* (CD) amplifier

- voltage gain is positive and less than unity (one), but current gain (and therefore power gain) can be very high

- voltage transfer characteristic ( $v_o$  vs.  $v_{in}$ ) has positive slope in saturation region because gain is positive

- output is taken from source terminal of MOSFET; output resistance  $\approx 1/g_m$  (typically, 10s to 100s of ohms)

- not necessary to include a resistor between drain terminal and  $V_{DD}$  (for NMOS) or between drain terminal and ground (for PMOS)

- can design source followers using NMOS or PMOS devices; small-signal model is the same for either device

# Common-gate (CG) amplifier

- noninverting

- voltage gain comparable to common-source amp;  $A_v = g_m(r_o||R_D||R_L)$  in the typical design

- gate terminal can be grounded directly (requires a bipolar power supply) or for signals only through a capacitor (capacitor blocks DC)

- input resistance  $\approx 1/g_m$  (typically, 10s to 100s of ohms)

### *n*-channel vs. *p*-channel MOSFETs (NMOS and PMOS)

- comparison of electron mobility  $\mu_n$  and hole mobility  $\mu_p$ ; hole mobility is approximately 0.25 to 0.5 times electron mobility for doped Si; thus, NMOS is faster than PMOS, and NMOS amps generally have more gain than PMOS amps for a given quiescent drain current  $I_D$

- $v_{GS}$ ,  $v_{DS}$ , and  $V_t$  are all negative for enhancement-mode PMOS, so  $v_{SG}$ ,  $v_{SD}$ , and  $|V_t|$  are often used in formulas instead

- $i_D$  is positive for both types (Sedra and Smith's convention), so  $i_{Dn}$  flows *into* the drain of an NMOS device, and  $i_{Dp}$  flows *out of* the drain of a PMOS device

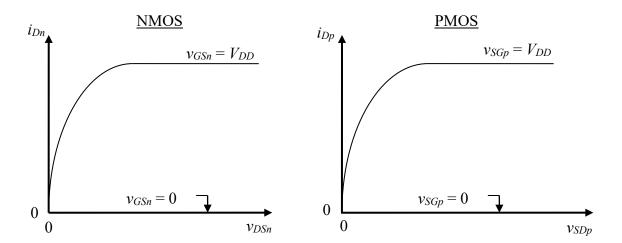

- *i-v* characteristics of NMOS and PMOS; curves for  $v_{GSn}$  or  $v_{SGp}$  with magnitudes less than  $V_{DD}$  lie between the horizontal axis and the ones for  $V_{DD}$ :

circuit symbols (enhancement-mode shown; pay attention to directions of arrows; PMOS symbol is often drawn "upside-down" with source terminal above drain terminal in circuit diagrams):

$$\underbrace{NMOS}_{D} \qquad \underbrace{PMOS}_{D}$$

$$G \longrightarrow B \text{ (substrate)} \qquad G \longrightarrow B \text{ (substrate)}$$

substrate (or body) internally connected to source:

$$G \longrightarrow S$$

$G \longrightarrow S$

symbols frequently used in digital logic gate literature:

$$G \rightarrow \bigcup_{S}^{D}$$

$G \rightarrow \bigcup_{S}^{D}$

- small-signal model is the same for NMOS and PMOS devices

- quiescent drain current of PMOS device with source degeneration resistor:

$$I_{D} = \frac{V_{DD} - V_{G} - \left| V_{tp} \right|}{R_{S}} + \frac{1}{k_{p}R_{S}^{2}} - \frac{1}{k_{p}R_{S}^{2}} \sqrt{1 + 2k_{p}R_{S} \left( V_{DD} - V_{G} - \left| V_{tp} \right| \right)}$$

### CMOS logic gates

- no resistors used

- negligible drain current ( $i_{Dp} \approx 0$  and  $i_{Dn} \approx 0$ ) after equilibrium is established after logical state change (assumes no significant current supplied to load connected to output terminal); true for *all* types of CMOS gates

- MOSFETs are in either cut-off ("off") or triode region ("on") in all logical states after equilibrium is reached

- MOSFETs in triode region have  $v_{DS} = 0$  because  $i_D = 0$  in equilibrium

- MOSFETs in cut-off region can have  $v_{DS} = 0$ ,  $|v_{DS}| = V_{DD}$ , or any other voltage

- during logical transitions, significant drain current flows and reaches a peak when MOSFETs are in the saturation region; the primary source of time-average dissipated power in CMOS gates is the brief current that flows during transitions; part of it flows through the PMOS and NMOS devices, and part of it charges/discharges gate capacitances of following logic gates through the drain-to-source resistance  $r_{DS}$  (hundreds to a few thousand ohms) that characterizes the triode region; dissipation in  $r_0$  in the saturation region is negligible

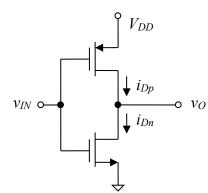

- CMOS inverter circuit (shown at right); as  $v_{IN}$  increases from 0 V to  $V_{DD}$ , the regions of operation progress through the following states:

| PMOS: triode     | NMOS: cut-off    |

|------------------|------------------|

| PMOS: triode     | NMOS: saturation |

| PMOS: saturation | NMOS: saturation |

| PMOS: saturation | NMOS: triode     |

| PMOS: cut-off    | NMOS: triode     |

- NAND and NOR gate circuits:

- MOSFET body effect

- PMOS substrate (body) tied to most pos. voltage in circuit (usually  $V_{DD}$ )

- $\circ$  NMOS substrate (body) tied to most neg. voltage in circuit (usually 0 V or  $V_{SS}$ )

- o when substrate is tied to source (always the case for discrete MOSFETs; sometimes the case for integrated MOSFETs), the source-to-substrate voltage is zero ( $v_{SB} = 0$ )

- o if  $v_{SB} \neq 0$ , then  $V_{tn}$  increases (NMOS) or  $V_{tp}$  becomes more negative (PMOS)

- body effect does not generally affect CMOS logic gate operation, but the change in  $V_{tn}$  or  $V_{tp}$  can affect operation of analog amplifiers

- o body effect also changes effective value of small-signal parameter  $g_m$ , which also affects operation of analog amplifiers

- Noise margins and input threshold voltages

- $\circ$   $V_{IL}$  = max. (threshold) input voltage considered to be a logical 0 (low)

- $\circ$   $V_{OL}$  = defined value of logical 0 (low) output; also min. input voltage considered to be a logical 0 (low); typically equal to 0 V in CMOS circuits

- $\circ$   $V_{IH}$  = min. (threshold) input voltage considered to be a logical 1 (high)

- o  $V_{OH}$  = defined value of logical 1 (high) output; also max. input voltage considered to be a logical 1 (high); typically equal to  $V_{DD}$  in CMOS circuits

- noise margins

- max. noise amplitude that can be added or subtracted to input voltage  $v_I$  of logic gate without affecting the interpretation of the input as a logical 0 or logical 1

- for CMOS inverter,  $V_{IL}$  and  $V_{IH}$  are defined as the input voltages at which the voltage transfer characteristic (VTC) has a slope of 1; similar definition for all other types of logic gates

- low-input noise margin:  $NM_L = V_{IL} V_{OL}$

- high-input noise margin:  $NM_H = V_{OH} V_{IH}$

- for CMOS inverter with matched PMOS and NMOS devices:

$$NM_{H} = \frac{1}{8} (3V_{DD} + 2V_{t})$$

$$NM_{L} = \frac{1}{8} (3V_{DD} + 2V_{t})$$

- CMOS output resistance

- o if  $|v_{DS}| \ll |v_{GS} V_t|$ , MOSFET acts like a voltage-controlled resistor (similar expression for PMOS):

o in triode region,

$$i_D = k_n \left[ \left( v_{GS} - V_t \right) v_{DS} - \frac{1}{2} v_{DS}^2 \right]$$

, but if  $|v_{DS}| << |v_{GS} - V_t|$ ,

$$i_D \approx k_n \left( v_{GS} - V_t \right) v_{DS} \quad \rightarrow \quad \frac{v_{DS}}{i_D} = r_{DS} = \frac{1}{k_n \left( v_{GS} - V_t \right)}$$

, where  $v_{GS} = V_{DD}$  usually

- o output resistance  $r_{DS}$  is the "R" in the RC time constant that governs charge/discharge rate of gate capacitances connected to output of logic gate

- O Note that  $r_{DS} \neq r_o$ ! The former applies in the triode region, the latter in the saturation region.

Fundamentals of BJT operation (focus is on *npn* type this semester)

- npn: thin p-type base sandwiched between n-type emitter and collector

- pnp: opposite of npn

- base-emitter (B-E) and collector-base (C-B) junctions are regular *pn* junctions and have many similarities to *pn* junction diodes (i.e., they can be forward or reverse-biased; they have turn-on voltages)

- turn-on voltage  $(V_F)$  is approx. 0.7 V for Si

- effect of changing base current  $i_B$

- effect of changing collector-emitter voltage  $v_{CE}$  (normally C-B junction is reverse biased or at least not heavily forward biased; necessary for collector current to flow)

- directions and polarities of important currents and voltages  $(i_B, i_C, i_E, v_{BE}, v_{CE})$

- thin base region allows electrons (npn) or holes (pnp) to flow from emitter to collector

- emitter more heavily doped than base allows base to fill with minority charge carriers (electrons for *npn*; holes for *pnp*) when base current flows; minority carriers are electrons in a *p*-type base or holes in an *n*-type base

- base-emitter junction is forward biased if  $v_{BE}$  is at turn-on voltage  $(V_F)$

- *i-v* characteristic of B-E junction is the same as that of a *pn*-junction diode:

$$i_B = I_{SB} \left( e^{v_{BE}/\eta V_T} - 1 \right),\,$$

where  $I_{SB}$  = saturation (scale) current of B-E junction,  $\eta$  = emission coefficient (typically assumed to equal one), and  $V_T$  = thermal voltage, which is given by

$$V_T = \frac{T}{11,600}$$

, where  $T =$  temperature in kelvins ( $V_T \approx 25$  mV at room temp.)

- collector-base junction is usually reverse biased (produces depletion region) or lightly forward biased; in either case, the built-in E field across the C-B junction is sufficiently strong to draw most of the minority carriers in the base into the collector

- collector current related to base current by  $i_C = \beta i_B$  in the active region, where  $\beta$  = forward DC current gain (values are typically 20–300, but vary among BJT types, even among individual units of a given type within the same manufacturing batch)

- $\beta$  varies strongly with temperature

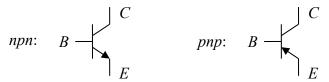

## BJT circuit symbols

pay attention to directions of arrows (arrow indicates the emitter terminal and BJT type; arrow of *npn* is "not pointing in"; arrow indicates direction of emitter current)

# *npn* vs. *pnp* BJTs

- $v_{BE}$  and  $v_{CE}$  of npn BJTs have positive values in normal operation

- $v_{BE}$  and  $v_{CE}$  of pnp BJTs have negative values in normal operation (use  $v_{EB}$  and  $v_{EC}$ , which are positive, instead)

- $i_B$  and  $i_C$  flow *into* base and collector terminals of npn BJTs and out of base and collector terminals of pnp BJTs

- *i<sub>E</sub>* flows *out of* emitter terminal of *npn* BJTs and *into* emitter terminal of *pnp* BJTs

- i-v characteristics of npn and pnp BJTs have voltages of opposite sign (unless  $v_{EB}$  and  $v_{EC}$  are used for pnp)

## General analysis techniques for BJT circuits

- during normal operation,  $v_{CE}$  (for npn BJTs) is always positive (negative for pnp; i.e.,  $v_{EC}$  is positive for pnp)

- $v_{BE} \approx 0.7 \text{ V (for Si } npn)$  in the active and saturation regions ( $v_{EB} \approx 0.7 \text{ V for Si } pnp$ )

- regions of operation for silicon *npn* BJTs ( $v_{CE|sat} \approx 0.2-0.3 \text{ V}$ ):

- o cut-off:  $v_{BE} < 0.7 \text{ V}$ ,  $i_B = i_C = 0$

- o active:  $v_{BE} \approx 0.7 \text{ V}$ ,  $i_C = \beta i_B$  and  $v_{CE} > v_{CE}|_{\text{sat}}$

- o saturation:  $v_{BE} \approx 0.7 \text{ V}$ ,  $i_C < \beta i_B$  and  $v_{CE} = v_{CE}|_{\text{sat}}$

- determination of region of operation (cutoff, active, or saturation)

- o if possible, determine whether base-emitter junction is forward biased; if not, then the BJT is in the cut-off region; if so, then active or saturation

- o assume BJT is in one region and analyze the circuit based on that assumption

- o check all voltages and currents and determine whether their values are consistent with the initial assumption. If so, analysis is complete. If not, use the results of the initial analysis to determine likely region of operation. Repeat analysis under new assumption and confirm.

- for more accurate analysis in active region (rarely necessary), use  $i_B = I_{SB} e^{v_{BE}/\eta V_T}$  and  $i_C = \beta I_{SB} e^{v_{BE}/\eta V_T}$  (omit "-1" because B-E junct. is forward biased), where  $I_{SB}$  = saturation (scale) current for B-E junction,  $\eta$  = emission coefficient (typically assumed to equal one), and  $V_T$  = thermal voltage

- by KCL,  $i_E = i_B + i_C$  (for *npn* and *pnp*)

### Relevant course material:

HW: #7, #8, and #9 (#9 is ungraded)

Labs: #4 and #5

Readings: Assignments from Nov. 5 through Dec. 8, including the supplemental readings:

"PMOS Small-Signal Model"

"Output Resistance of CMOS Inverter"

This exam will focus primarily on the following course outcomes and related topics:

5. Determine the region of operation of a MOSFET or BJT [focus on PMOS and BJTs].

- 6. Determine and/or set the bias point (quiescent operating point) of a MOSFET or BJT circuit. [focus on PMOS; biasing of BJT not covered on exam]

- 7. Find transfer functions of basic MOSFET and/or BJT amplifier circuits, switching circuits, and digital logic circuits [focus on PMOS devices, CMOS digital circuits, and NMOS or PMOS amplifiers, possibly with *r<sub>o</sub>* included].

The course outcomes are listed on the Course Policies and Information sheet, which was distributed at the beginning of the semester and is available on the Syllabus and Policies page at the course web site. The outcomes are also listed on the Course Description page. Note, however, that some topics not directly related to the course outcomes could be covered on the exam as well.