# JEDEC STANDARD

# JEDEC Dictionary of Terms for Solid-State Technology – 7<sup>th</sup> Edition

JESD88F (Revision of JESD88E, June 2013)

FEBRUARY 2018

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

# NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to <u>www.jedec.org</u> under Standards and Documents for alternative contact information.

Published by ©JEDEC Solid State Technology Association 2018 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

# **PRICE: Contact JEDEC**

Printed in the U.S.A. All rights reserved

# PLEASE!

# DON'T VIOLATE THE LAW!

This document is copyrighted by JEDEC and may not be reproduced without permission.

For information, contact:

JEDEC Solid State Technology Association 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

or refer to www.jedec.org under Standards-Documents/Copyright Information.

Downloaded by Kenneth Hass (kjh016@bucknell.edu) on Apr 20, 2018, 10:19 am PDT

Bucknell

# Foreword

This dictionary was originally prepared and edited by a special Working Group consisting of JEDEC consultants Fred A. Mann and Frank S. Stein, under the direction of the JEDEC Board of Directors, and is periodically updated by JEDEC Committee JC-10 on Terms, Definitions, and Symbols. After the 1<sup>st</sup> edition, regular contribution has been made by David Sweetman. Publication of the JEDEC Dictionary was approved by the JEDEC Board of Directors under Ballot JCB-00-97.

This Seventh Edition includes definitions from 26 standards that were not included in the Sixth Edition plus revised definitions from 32 additional publications and standards that have been updated. All reported errors and necessary rewording have been taken into account.

#### Introduction

As new or revised JEDEC or Joint publications<sup>\*</sup> are issued, their definitions are considered for inclusion in this dictionary. All publications with definitions in this edition of the dictionary are listed in Annex A. The following are often not included: (1) terms having a specialized meaning only within the context of a particular publication (usually a test method), e.g., "brush: A toothbrush with a handle made up of nonreactive material ..."; and (2) concepts where the publication gives only a symbol and a term but no definition. This dictionary, like any dictionary, is primarily intended to define concepts. For an extensive list of symbols and abbreviations with the corresponding terms for many variations (dc, peak, rms, small signal, large signal, etc.), see JEP104, *Reference Guide to Letter Symbols for Semiconductor Devices*.

All entries are reviewed for punctuation, grammar, and clarity, as well as for accuracy, and reworded if such is considered warranted. If a definition is substantially recast, the date of the source publication is followed by a pound sign (#). The editors have made every effort to ensure that the *intent* of the original definition is retained in all cases. When the same term is defined in more than one source publication in substantially different words having essentially equivalent meanings, the formulation is selected that, in the opinion of the editors, is the most completely and clearly stated, and the pound sign is applied to the references to the other publications. If the same term is defined with different meanings in two or more publications, all forms are given in alphanumeric order by publication reference. The definitions are numbered  $(1), (2), \ldots$ , but no order of preference is intended.

While most of the conventions used in this dictionary are self-explanatory, three may need further explanation: (1) Terms separated by semicolons (;) are synonyms. (2) Square brackets [] enclosing a part of a term and possibly parts of its definition indicate that the words placed between them may replace all or some of the preceding words. Selection of the bracketed part of the term requires the selection of the bracketed parts of the definition. This convention is used to show at first sight the construction of terms having parallel definitions. (3) Parentheses () enclosing a part of a term indicate that the part of the term placed between them may be omitted if, in the context in which the term is used, no confusion is likely.

# EXAMPLE Darlington (transistor)

The parentheses indicate that the term "Darlington" can be used alone as having the same meaning as "Darlington transistor".

<sup>\*</sup> As used in this dictionary, the word "publication" is a generic term that includes standards.

#### Scope

Each term and definition in this dictionary has been included strictly for application within the solid-state industry. Many of the terms and definitions in this dictionary may have applicability beyond the scope of the JEDEC Solid State Technology Association; however, an assumption of such extended applicability is the responsibility of the user. The goal is to include the appropriate terms and definitions from all JEDEC publications and standards. At the present time, only terms and definitions from the publications listed in Annex A are included.

Bucknell

# JEDEC DICTIONARY OF TERMS FOR SOLID-STATE TECHNOLOGY

| Terms, abbreviations, letter symbols, and definitions                                                                                                                                                                                                                                                          | References                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Α                                                                                                                                                                                                                                                                                                              |                                      |

| A: See "port A; port B".                                                                                                                                                                                                                                                                                       |                                      |

| A; a: See "anode terminal".                                                                                                                                                                                                                                                                                    |                                      |

| abbreviation: A shortened form of a word or expression.                                                                                                                                                                                                                                                        | JESD77D, 8/12<br>JESD99C, 12/12      |

| <b>ABD:</b> See "avalanche breakdown diode".                                                                                                                                                                                                                                                                   |                                      |

| <b>ABD array:</b> A device having three or more terminals and containing multiple diodes within a single package, with at least one of the diodes being an ABD.                                                                                                                                                | JESD77D, 8/12<br>JESD210A, 3/17      |

| NOTE ABD arrays can be classified as (1) devices with multiple discrete semiconductor chips; and (2) devices with multiple diode junctions diffused into a single semiconductor chip.                                                                                                                          |                                      |

| abort: An operation that stops the currently running operation on the memory module                                                                                                                                                                                                                            | JESD245B, 4/17                       |

| <b>above-passivation layer (APL)</b> : A low-impedance metal plane, built on the surface of a die above the passivation layer, that connects a group of bumps or pins (typically power or ground).                                                                                                             | JS-001-2017, 5/17                    |

| NOTE This structure is sometimes referred to as a redistribution layer (RDL). There may be multiple APLs (sometimes referred to as islands) for a power or ground group.                                                                                                                                       |                                      |

| absolute accuracy error: Synonym for "total error".                                                                                                                                                                                                                                                            | JESD99C, 12/12                       |

| <b>absolute maximum rated hot-spot temperature (of a module):</b> The maximum temperature of the hottest element within any component or die within a module, beyond which damage (latent or otherwise) may occur; it is frequently specified by device manufacturers for a specific device and/or technology. | JESD226, 1/13                        |

| NOTE 1 The hot spot is typically a transistor junction, channel, or power dissipating element.                                                                                                                                                                                                                 |                                      |

| NOTE 2 Manufacturers may also specify maximum case temperatures for specific packages if the hot spot to case differential is known.                                                                                                                                                                           |                                      |

| <b>absolute maximum rated junction temperature:</b> The maximum junction temperature of an operating device, as listed in its data sheet and beyond which damage (latent or otherwise) may occur; it is frequently specified by device manufacturers for a specific device and/or technology.                  | JEP163, 9/15<br>JESD22-A108 F, 4/17  |

| NOTE Manufacturers may also specify maximum case temperatures for specific packages.                                                                                                                                                                                                                           |                                      |

| <b>absolute maximum rated RF input power:</b> The maximum applied RF signal to the module input, beyond which damage (latent or otherwise) may occur; it is frequently specified by device manufacturers for a specific device and/or technology.                                                              | JESD226, 1/13                        |

| <b>absolute maximum rated temperature:</b> The maximum junction or ambient temperature of an operating device, as listed in its data sheet and beyond which damage (latent or otherwise) may occur.                                                                                                            | JESD89-1A, 10/07<br>JESD89-3A, 11/07 |

NOTE Manufacturers may also specify maximum case temperatures for specific packages.

| <b>absolute maximum rated voltage:</b> The maximum voltage that may be applied to a device, as listed in its data sheet and beyond which damage (latent or otherwise) may occur; it is frequently specified by device manufacturers for a specific device and/or technology.                                                                                                                                                                                                                                                                                                                  | JEP163, 9/15<br>JESD22-A108 F, 4/17<br>JESD89-1A, 10/07#<br>JESD89-2A, 10/07#<br>JESD89-3A, 11/07#<br>JESD226, 1/13# |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| absolute maximum rating: Synonym for "maximum rating".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JESD77D, 8/12                                                                                                        |

| <b>ABTXXXXXX series:</b> A BiCMOS series that includes devices whose input logic levels are TTL-compatible and whose outputs are specified at TTL levels.                                                                                                                                                                                                                                                                                                                                                                                                                                     | JESD54, 2/96                                                                                                         |

| accelerated ELF test time $(t_A)$ : The duration of the accelerated ELF test.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JESD74A, 2/07                                                                                                        |

| <b>accelerated equivalent soak:</b> A soak at a higher temperature for a shorter time (compared to the standard soak) to provide roughly the same amount of moisture absorption.                                                                                                                                                                                                                                                                                                                                                                                                              | J-STD-020E, 1/15                                                                                                     |

| accelerated soft error rate (ASER): A soft error rate in the presence of an intense ionizing radiation source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JESD89, 8/01                                                                                                         |

| <b>acceleration factor</b> ( <i>A</i> , <b>AF</b> ): For a given failure mechanism, the ratio of the time it takes for a certain fraction of the population to fail, following application of one stress or use condition, to the corresponding time at a more severe stress or use condition.                                                                                                                                                                                                                                                                                                | JEP122H, 9/16<br>JEP143C, 7/12<br>JEP163, 9/15<br>JESD74A, 2/07#                                                     |

| NOTE 1 Times are generally derived from modeled time-to-failure distributions (lognormal, Weibull, exponential, etc.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JESD85, 7/01#<br>JESD91A, 8/01#<br>JESD94B, 10/15                                                                    |

| NOTE 2 Acceleration factors can be calculated for temperature, electrical, mechanical, environmental, or other stresses that can affect the reliability of a device.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                      |

| NOTE 3 Acceleration factors are a function of one or more of the basic stresses that can cause one or more failure mechanisms. For example, a plot of the natural log of the time-to-failure for a cumulative constant percentage failed (e.g., 50%) at multiple stress temperatures as a function of $1/kT$ , the reciprocal of the product of Boltzmann's constant in electronvolts per kelvin and the absolute temperature in kelvins, is linear if one and only one failure mechanism is involved. The best-fit linear slope is equal to the apparent activation energy in electronvolts. |                                                                                                                      |

| NOTE 4 The abbreviation AF is often used in place of the symbol A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| acceleration factor, stress $(A_f)$ : The acceleration factor due to the presence of some stress (e.g., current density, electric field, humidity, temperature cycling).                                                                                                                                                                                                                                                                                                                                                                                                                      | JEP122H, 9/16<br>JEP143C, 7/12                                                                                       |

# Terms, abbreviations, letter symbols, and definitions

# # The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

# References

#### Terms, abbreviations, letter symbols, and definitions

#### acceleration factor, temperature $(A_T)$ : The acceleration factor due to changes in temperature.

NOTE 1 This is the acceleration factor most often referenced. The Arrhenius equation for reliability is commonly used to calculate the acceleration factor that applies to the acceleration of time-to-failure distributions for microcircuits and other semiconductor devices:

$$A_{\rm T} = \lambda_{\rm T1} / \lambda_{\rm T2} = \exp[(-E_{\rm aa}/k)(1/T_1 - 1/T_2)]$$

where

$E_{aa}$  is the apparent activation energy (eV); k is Boltzmann's constant (8.62 × 10<sup>-5</sup> eV/K);  $T_1$  is the absolute temperature of test 1 (K);  $T_2$  is the absolute temperature of test 2 (K);

$\lambda_{T1}$  is the observed failure rate at test temperature  $T_1$  (h<sup>-1</sup>);

$\lambda_{\rm T2}$  is the observed failure rate at test temperature  $T_2$  (h<sup>-1</sup>).

NOTE 2 The best-fit linear slope of a plot of the natural log of the time-to-failure as a function of 1/kT, the reciprocal of the product of Boltzmann's constant in electronvolts per kelvin and the absolute temperature in kelvins, is equal to the apparent activation energy in electronvolts.

| NOTE 3        | $\lambda_q = \lambda_0 \cdot A_T$ , where $\lambda_q$ is the quoted (predicted) system failure rate at some system temperature $T_s$ , $\lambda_o$ |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| is the obser  | rved failure rate at some test temperature $T_t$ , and $A_T$ is the temperature acceleration factor from $T_t$ to                                  |

| $T_{\rm s}$ . |                                                                                                                                                    |

acceleration factor, voltage  $(A_v)$ : The acceleration factor due to changes in voltage.

acceleration model: A mathematical formulation of the relationship between (1) the rate (speed) of a degradation mechanism or the time-to-failure and (2) the conditions or stresses that caused the degradation. JEP143C, 7/12 JEP148B, 1/14

| accelerometer: An electronic device that converts mechanical deformation of an internal structure | JS9703, 3/09 |

|---------------------------------------------------------------------------------------------------|--------------|

| caused by acceleration into electrical signals that can be sensed by a data acquisition system.   |              |

| acceptance inspection: A sampling inspection or series of sampling inspections used to determine | JESD16-A, 4/95 |

|--------------------------------------------------------------------------------------------------|----------------|

| the suitability of a lot of material for shipment.                                               |                |

**accept number:** The maximum number of nonconforming components in the sample for which JESD16-A, 4/95 acceptance of the lot is allowed under the sampling plan.

**access time:** The time interval between the application of a specific input pulse and the availability JESD100B.01, 12/02 of valid signals at an output.

**ac controller:** A circuit that produces, from an ac input, an ac output that is proportional to a JESD14, 11/86# control input.

**accumulator:** A register in which one operand of an operation can be stored and subsequently JESD100B.01, 12/02 replaced by the result of another operation. (Ref. IEC 824.)

**accuracy:** The difference between the sample estimate and the population parameter being JEP132, 7/98 JESD557C, 4/15

AC LED: An LED designed to be driven by a sinusoidal alternating current (AC) power source, typically having an operational frequency and voltage equal to the frequency and voltage of the mains (50/60 Hz, 230/120 V).

# The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

#### References

JEP122H, 9/16

JEP143C, 7/12

JEP143C, 7/12 JESD74A, 2/07

JEP163, 9/15 JESD74A, 2/07#

# JEDEC Standard No. 88F Page 4

# Terms, abbreviations, letter symbols, and definitions

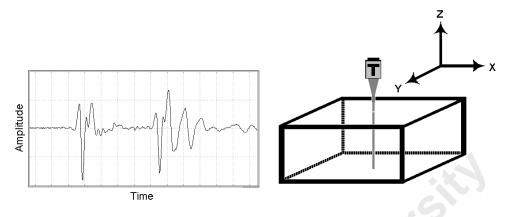

**acoustic data, A-mode:** Acoustic data collected at the smallest X-Y-Z region defined by the limitations of the given acoustic microscope. An A-mode display contains amplitude and phase/polarity information as a function of time of flight at a single point in the X-Y plane.

**Example of A-mode display**

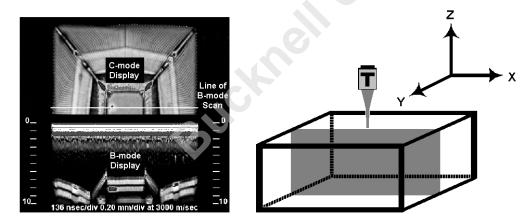

**acoustic data, B-mode:** Acoustic data collected along an X-Z or Y-Z plane versus depth (Z) using a reflective acoustic microscope. A B-mode scan contains amplitude and phase/polarity information as a function of time of flight at each point along the scan line. A B-mode scan furnishes a two-dimensional (cross-sectional) description along a scan line (X or Y).

J-STD-035, 5/99

Example of B-mode display (bottom half of picture on left)

# The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

# References

J-STD-035, 5/99

#### Terms, abbreviations, letter symbols, and definitions

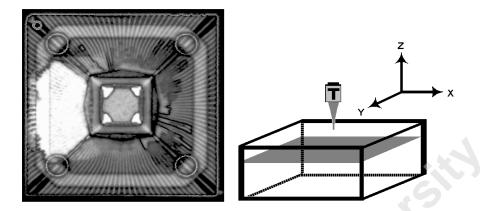

**acoustic data, C-mode:** Acoustic data collected in an X-Y plane at depth Z using a reflective acoustic microscope. A C-mode scan contains amplitude and phase/polarity information at each point in the scan plane. A C-mode scan furnishes a two-dimensional (area) image of echoes arising from reflections at a particular depth (Z).

Example of C-mode display

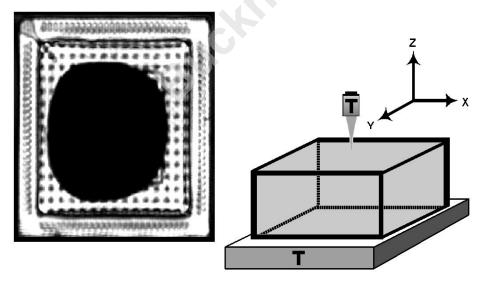

**acoustic data, through-transmission mode:** Acoustic data collected in an X-Y plane throughout the depth (Z) using a through-transmission acoustic microscope. A through-transmission mode scan contains only amplitude information at each point in the scan plane. A through-transmission scan furnishes a two-dimensional (area) image of transmitted ultrasound through the complete thickness/depth (Z) of the sample or component.

J-STD-035, 5/99

Example of through-transmission display

acoustic microscope: Equipment that creates an image using ultrasound to view a specimen's surface or subsurface features,

J-STD-020E, 1/15

# The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

# References

J-STD-035, 5/99

| Terms, abbreviations, letter symbols, and definitions                                                                                                                                                                                                                                                                                             | References                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| ac terminal: A terminal that is to be connected to the ac circuit.                                                                                                                                                                                                                                                                                | JESD14, 11/86                                  |

| ac test: The process of verifying the specified timing of a device.                                                                                                                                                                                                                                                                               | JESD12-1B, 8/93<br>JESD99C, 12/12              |

| NOTE Testing of propagation delays, minimum setup and hold times, minimum pulse durations, etc., can be performed by using test vectors applied at the specified operating frequency of the device. Propagation delays of critical logic paths for system operation can be measured individually.                                                 | JE3D99C, 12/12                                 |

| activation energy $(E_a)$ : The excess free energy over the ground state that must be acquired by an atomic or molecular system in order that a particular process can occur.                                                                                                                                                                     | JEP122H, 9/16<br>JEP143C, 7/12<br>JEP163, 9/15 |

| NOTE The activation energy is used in the Arrhenius equation for the thermal acceleration of physical reactions. The term "activation energy" is not applicable when describing thermal acceleration of time-to-failure distributions, e.g., in the Arrhenius equation for reliability; hence the need for the term "apparent activation energy". | JESD91A, 8/01<br>JESD85, 7/01                  |

| active circuit element: See "circuit element, active".                                                                                                                                                                                                                                                                                            |                                                |

| <b>active desiccant:</b> Desiccant that is either fresh (new) or has been baked according to the manufacturer's recommendations to renew it to original specifications.                                                                                                                                                                           | J-STD-033C, 2/12                               |

| active device: A device in which at least one circuit element is an active circuit element.                                                                                                                                                                                                                                                       | JESD99C, 12/12                                 |

| active element: See "circuit element, active".                                                                                                                                                                                                                                                                                                    |                                                |

| <b>active-pulldown output:</b> A bipolar (three-state or totem-pole) output whose source-current capability significantly exceeds its sink-current capability.                                                                                                                                                                                    | JESD99C, 12/12                                 |

| <b>active-pullup output:</b> A bipolar (three-state or totem-pole) output whose sink-current capability significantly exceeds its source-current capability.                                                                                                                                                                                      | JESD99C, 12/12                                 |

| <b>ac unbalanced voltage:</b> The difference between the peak values of the ac voltages at the two outputs when the circuit is operating in the maximum-output-voltage-swing condition.                                                                                                                                                           | JESD99C, 12/12                                 |

| ADC: See "analog-to-digital [A/D] converter".                                                                                                                                                                                                                                                                                                     |                                                |

| <b>address:</b> (1) A character or group of characters that identifies a register, a particular part of storage, or some other data source or destination. (Ref. ANSI X3.172.)                                                                                                                                                                    | JESD100B.01, 12/02<br>JESD230C, 11/16          |

| NOTE 1 In a nonvolatile memory array, the address consists of characters, typically hexadecimal, to identify the row and column location of the memory cell(s).                                                                                                                                                                                   |                                                |

| NOTE 2 For NAND nonvolatile memory devices, the row address is for a page, block, or logical unit number (LUN); the column address is for the byte or word within a page.                                                                                                                                                                         |                                                |

| NOTE 3 The least significant bit of the column address is zero for the source synchronous data interface.                                                                                                                                                                                                                                         | IESD100D 01 10/02                              |

| (2) To refer to a device or a data item by its address. (Ref. ANSI X3.172.)                                                                                                                                                                                                                                                                       | JESD100B.01, 12/02                             |

| <b>address data input/output [ADQ(n)]:</b> The pins that are multiplexed three ways to serve as address input, data input, and data output pins. When the address data input/output numbering is significant for device operation, the addresses are numbered beginning with 0.                                                                   | JESD21-C, 1/97                                 |

<sup>#</sup> The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

| Terms, abbreviations, letter symbols, and definitions                                                                                                                                                                                                                                                                                                       | References         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| <b>address inputs</b> $[A(n)]$ : Those inputs that select (address) a particular cell or set of cells within a memory array for presentation on the device outputs. The integer (n) serves to differentiate the address inputs, one from another. When the address number is significant for device operation, the addresses are numbered beginning with 0. | JESD21-C, 1/97     |

| <b>address latch enable (AL):</b> An input that, when true, allows the input address to be entered into a register and, when false, causes the address state previously entered to be latched.                                                                                                                                                              | JESD21-C, 1/97     |

| address register: A register that is used to hold an address. (Ref. IEC 824.)                                                                                                                                                                                                                                                                               | JESD100B.01, 12/02 |

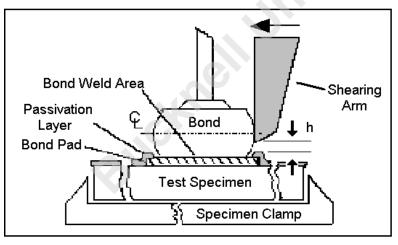

| <b>adhesion strength:</b> The force needed to separate two materials by a defined method like shear or pull.                                                                                                                                                                                                                                                | JESD167, 4/13      |

| <b>ADQ(n):</b> See "address data input/output".                                                                                                                                                                                                                                                                                                             |                    |

| affected customer (of a disaster): Any organization that                                                                                                                                                                                                                                                                                                    | JESD246, 1/14      |

| 1) is to receive product from the supplier, but the agreed-to shipment date of that product is impacted due to a disaster, and that organization has a contract or purchase agreement with disaster notification requirements;                                                                                                                              |                    |

| 2) has requested (and the supplier has agreed to provide) disaster notifications; or                                                                                                                                                                                                                                                                        |                    |

| 3) is an approved supplier agent.                                                                                                                                                                                                                                                                                                                           |                    |

| air ionizer: A source of charged air molecules (ions).                                                                                                                                                                                                                                                                                                      | JESD625B, 1/12     |

| AL: See "address latch enable".                                                                                                                                                                                                                                                                                                                             |                    |

| ALARA principle: Acronym for "As Low As Reasonably Achievable".                                                                                                                                                                                                                                                                                             | JEP151, 12/15      |

| NOTE This principle in radiation protection states that exposure to ionizing radiation should be kept as low as possible, even lower than prescribed by legal requirements, if this is achievable.                                                                                                                                                          |                    |

| alignment mark: Synonym for "registration mark".                                                                                                                                                                                                                                                                                                            | JESD99C, 12/12     |

| "A" limit: The more positive (less negative) limit of a range of some quantity.                                                                                                                                                                                                                                                                             | JESD99C, 12/12     |

| <b>alpha activity (of a source):</b> The number of alpha particles produced by the decay of the alpha source per unit time.                                                                                                                                                                                                                                 | JESD89-2A, 10/07   |

| NOTE The preferred SI unit is the becquerel (Bq); to convert curies to becquerels, multiply the number of curies by $3.7 \times 10^{10}$ Bq (exactly).                                                                                                                                                                                                      |                    |

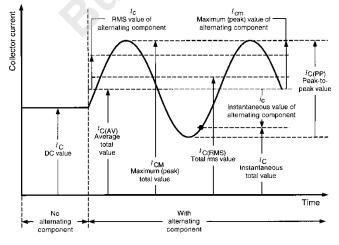

| <b>alternating current (ac):</b> (1) An electric current that reverses direction at regularly recurring intervals of time.                                                                                                                                                                                                                                  | IEEE Std 100       |

| (2) The voltage bias applied at alternating current bias conditions.                                                                                                                                                                                                                                                                                        | JESD241, 12/15     |

| <b>alternative method:</b> For a device requirement that has a prescribed method to verify compliance, another method that has been verified through test and analysis to adequately verify compliance of the device with that requirement.                                                                                                                 | JESD93, 9/05       |

ALU: See "arithmetic and logic unit".

<sup>#</sup> The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

| Terms, abbreviations, letter symbols, and definitions                                                                                                                                                                                                                                                                                                                                                                                | References                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| ambient temperature; free-air temperature $(T_A)$ : The air temperature measured below a device, in an environment of substantially uniform temperature, cooled only by natural air convection and not materially affected by reflective and radiant surfaces.                                                                                                                                                                       | JESD10, 1/76<br>JESD77D, 8/12<br>EIA323, 3/66 |

| A-mode: See "acoustic data, A-mode".                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| A(n): See "address inputs".                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| analog gate: A gate whose output signal is a linear function of one or more input signals.                                                                                                                                                                                                                                                                                                                                           | JESD99C, 12/12                                |

| <b>analog-to-digital [A/D] converter (ADC):</b> A converter that uniquely represents all analog input values within a specified total input range by a limited number of digital output codes, each of which exclusively represents a fractional part of the total analog input range.                                                                                                                                               | JESD99C, 12/12                                |

| NOTE This quantization procedure introduces inherent errors of $\pm \frac{1}{2}$ LSB (least significant bit) in the representation because, within this fractional range, only one analog value can be represented free of error by a single digital output code.                                                                                                                                                                    |                                               |

| <b>analog-to-digital processor:</b> An integrated circuit providing the analog part of an analog-to-digital converter.                                                                                                                                                                                                                                                                                                               | JESD99C, 12/12                                |

| NOTE Provision of external timing, counting, and arithmetic operations is necessary for implementing a full analog-to-digital converter.                                                                                                                                                                                                                                                                                             |                                               |

| <b>analysis of variance (ANOVA):</b> A statistical tool that allows for the comparison of more than two groups of data and provides valid assumptions. Computations of ANOVA involve partitioning total variation into two components: the variation from differences among group "means", and random variations within the groups known as "error". ANOVA provides for reliable results even when certain assumptions are violated. | JEP132, 7/98                                  |

| annular ring: The metallization pad area around the top or bottom of a castellation hole.                                                                                                                                                                                                                                                                                                                                            | JESD9C, 5/17                                  |

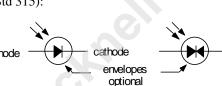

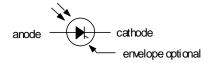

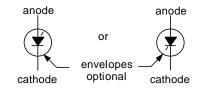

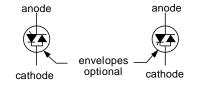

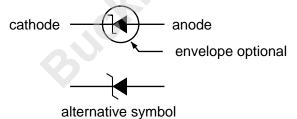

| anode: (1) The p-type region from which the forward current flows within a semiconductor diode.                                                                                                                                                                                                                                                                                                                                      | JESD77D, 8/12                                 |

| NOTE In Schottky diodes, usually the barrier metal replaces the p-type semiconductor region and the remaining semiconductor region is n-type; however, some Schottky diodes have been made with the barrier metal replacing the n-type semiconductor region, in which case the remaining semiconductor region is p-type.                                                                                                             | JESD282B.01, 11/02                            |

| (2) A circuit element to which positive bias is applied.                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| NOTE For the purpose of JEP154, when the die is the anode the electron flow is from the substrate through the solder bump to the die.                                                                                                                                                                                                                                                                                                | JEP154, 1/08                                  |

| (3) An electrode of an LED that, in the forward mode of operation, is connected to a positive potential with respect to the potential of the cathode electrode.                                                                                                                                                                                                                                                                      | JESD51-53, 5/12                               |

| NOTE In the case of a single p-n-junction diode, the anode electrode of the package is in ohmic contact with the p-doped side of the semiconductor p-n junction.                                                                                                                                                                                                                                                                     |                                               |

| <b>anode-cathode voltage; anode voltage (of a unidirectional thyristor):</b> The voltage between the anode and cathode terminals.                                                                                                                                                                                                                                                                                                    | JESD77D, 8/12                                 |

| NOTE The anode-cathode voltage is called "positive" when the anode potential is higher than the cathode potential and called "negative" when the anode potential is lower than the cathode potential.                                                                                                                                                                                                                                |                                               |

| anode current: Synonym for "forward current".                                                                                                                                                                                                                                                                                                                                                                                        | JESD77D, 8/12                                 |

<sup>#</sup> The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

References

JESD77D, 8/12

JESD210A, 3/17

JESD211.01, 11/12

JESD282B.01, 11/02

#### Terms, abbreviations, letter symbols, and definitions

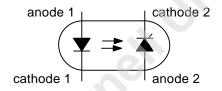

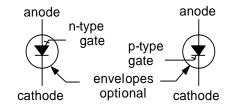

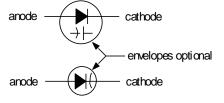

**anode terminal** (A, a) (1) (**general**): The terminal connected to the p-type region of the p-n junction or, when two or more p-n junctions are connected in series and have the same polarity, to the extreme p-type region.

NOTE 1 See note to "anode".

NOTE 2 This definition does not apply to current-regulator diodes.

commands and task management function requests in the host.

NOTE 3 For voltage-reference diodes, any temperature-compensation diodes that may be included shall be ignored in the determination of the anode terminal.

NOTE 4 For unidirectional blocking or low-capacitance ABDs, any rectifier diode(s) that may be included are ignored in the determination of the anode terminal.

anode \_\_\_\_\_ cathode \_\_\_\_\_ forward current

| (2) (of a current-regulator diode): The terminal to which current flows from the external circuit when the diode is biased to operate as a current regulator.                                                                                                                                                                      | JESD77D, 8/12                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| (3) (of a unidirectional diode thyristor): The terminal to which the current flows from the external circuit when the thyristor is in the on state.                                                                                                                                                                                | JESD77D, 8/12                                                   |

| (4) (of a unidirectional triode thyristor): The main terminal to which the principal current flows from the circuit being controlled when the thyristor is in the on state.                                                                                                                                                        | JESD77D, 8/12                                                   |

| NOTE A second anode terminal may be provided for connecting to the control circuit of an n-gate thyristor.                                                                                                                                                                                                                         |                                                                 |

| ANOVA: See "analysis of variance". See also "variance components analysis".                                                                                                                                                                                                                                                        |                                                                 |

| antistatic material: Material that inhibits triboelectric charging.                                                                                                                                                                                                                                                                | JESD625B, 1/12                                                  |

| NOTE The antistatic property of a material does not necessarily correlate with the resistivity or resistance of the material. Unlike the dissipative and conductive properties, antistatic is not defined by a measurable resistance range.                                                                                        |                                                                 |

| AOQ: See "average outgoing quality".                                                                                                                                                                                                                                                                                               |                                                                 |

| <b>APL:</b> See "above passivation layer".                                                                                                                                                                                                                                                                                         |                                                                 |

| <b>apparent activation energy</b> ( $E_{aa}$ ): An energy value, analogous to activation energy, that can be inserted in the Arrhenius equation for reliability to calculate an acceleration factor applicable to changes with temperature of time-to-failure distributions.                                                       | JEP122H, 9/16<br>JEP143C, 7/12<br>JEP163, 9/15<br>JESD74A, 2/07 |

| NOTE 1 An apparent activation energy should be associated with a specific failure mechanism and an observed time-to-failure distribution to calculate the acceleration factor for converting the observed failure rate to the quoted failure rate at a different temperature.                                                      | JESD85, 7/01#                                                   |

| NOTE 2 An activation energy is a measure of the heat energy needed to establish the rate of reaction for a specific failure mechanism. The reaction rate and other contributing factors, e.g., radiation, voltage, humidity, magnetic fields, determine the unique time-to-failure distribution for the modeled failure mechanism. |                                                                 |

| NOTE 3 The apparent activation energy is empirically determined from the change in an observed time-to-<br>failure distribution with temperature.                                                                                                                                                                                  |                                                                 |

| application client: An entity that is the source of Small Computer System Interface (SCSI)                                                                                                                                                                                                                                         | JESD220-1A, 3/16                                                |

<sup>#</sup> The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

| Terms, abbreviations, letter symbols, and definitions                                                                                                                               | References                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| <b>application requirements for quality and reliability:</b> The quality and reliability properties of the product required for the specified use conditions.                       | JEP148B, 1/14                       |

| <b>application-specific integrated circuit (ASIC):</b> An integrated circuit developed and produced for a specific application or function and for a single customer.               | JESD99C, 12/12                      |

| NOTE ASICs generally use standard cell or gate array design methodology.                                                                                                            |                                     |

| <b>application-specific standard product (ASSP):</b> An integrated circuit developed and produced for a specific application or function but made available for multiple customers. | JESD99C, 12/12                      |

| <b>application use conditions:</b> The full environmental and/or operating ranges that the application is specified to function within.                                             | JEP149, 11/04                       |

| <b>approved supplier agent:</b> A direct sales channel, an authorized manufacturer's representative, or an authorized distributor.                                                  | J-STD-046, 7/16<br>J-STD-048, 11/14 |

| arc: A visual anomaly that is a curved scratch.                                                                                                                                     | JESD22-B118, 3/11                   |

| <b>area array component:</b> A component that has terminations arranged in a grid on the bottom of the package and contained within the component outline.                          | JS9704A, 1/12                       |

| <b>area array package:</b> A package that has terminations arranged in a grid on the bottom of the package and contained within the package outline.                                | J-STD-020E, 1/15                    |

| <b>arithmetic and logic unit (ALU):</b> The part of a processor that performs arithmetic operations and logic operations. (Ref. IEC 824.)                                           | JESD100B.01, 12/02                  |

| arithmetic unit: The part of a processor that performs arithmetic operations. (Ref. IEC 824.)                                                                                       | JESD100B.01, 12/02                  |

| NOTE This term is sometimes used for a unit that performs both arithmetic and logic operations.                                                                                     |                                     |

| arm: An operation that enables or disables trigger(s) for a catastrophic save operation.                                                                                            | JESD245B, 4/17                      |

| <b>array density (of a gate array):</b> The number of available gates divided by the entire chip area.<br>NOTE Units are gates per unit area.                                       | JESD12-1B, 8/93<br>JESD99C, 12/12   |

| array, logic: Synonym for "gate array integrated circuit".                                                                                                                          | JESD99C, 12/12                      |

| <b>array-type package:</b> A package having a rectangular- or square-shaped body with or without chamfered corners and with perpendicular sides.                                    | JESD30H, 8/17                       |

References

JEP143C, 7/12

JESD91A, 8/01

#### Terms, abbreviations, letter symbols, and definitions

**Arrhenius equation (for reliability):** An equation used to calculate thermal acceleration factors for semiconductor device time-to-failure distributions:

$$A_{\rm T} = \lambda_{\rm T1} / \lambda_{\rm T2} = \exp \left[ (-E_{\rm aa} / k) (1 / T_1 - 1 / T_2) \right]$$

where

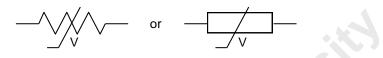

$A_{\rm T}$  is the acceleration factor due to changes in temperature;  $\lambda_{T1}$  is the observed failure rate at test temperature  $T_1$  (h<sup>-1</sup>);  $\lambda_{T2}$  is the observed failure rate at test temperature  $T_2$  (h<sup>-1</sup>);  $E_{aa}$  is the apparent activation energy (eV); k is Boltzmann's constant (8.62  $\times$  10<sup>-5</sup> eV/K);  $T_1$  is the absolute temperature of test 1 (K);  $T_2$  is the absolute temperature of test 2 (K). NOTE 1 The original Arrhenius equation (for atomic or molecular processes and chemical reactions) used the gas constant, not an activation energy, in the exponent. The "Arrhenius equation (for reliability)", used to calculate a thermal acceleration factor for a given observed time-to-failure distribution and  $E_{aa}$ , is in the form of the quotient of two Arrhenius equations, so that the acceleration factor from one temperature to another can be calculated. NOTE 2  $\lambda_q = \lambda_0 \cdot A_T$ , where  $\lambda_q$  is the quoted (predicted) system failure rate at some system temperature  $T_s, \lambda_o$ is the observed failure rate at some test temperature  $T_t$ , and  $A_T$  is the temperature acceleration factor from  $T_t$  to  $T_{\rm s}$ . ART: See "auto-load read transfer". artwork: The original, accurately scaled, oversize drawings and plastic overlays of the microcircuit JESD99C, 12/12 topological layout that are used to produce the master mask plates. NOTE Artwork has largely been supplanted by computer-produced drawings and masks. **ASER:** See "accelerated soft error rate". ASIC: See "application-specific integrated circuit". assembled state (of a component): The state of a component that has been attached to a second-JEP148B, 1/14 JEP156. 3/09 level assembly. JEP158, 11/09 assembly, microelectronic: See "microelectronic assembly". assignable cause: Synonym for "special cause". associated non-supply pin: A non-supply pin (typically an input, output, or I/O pin) that is JS-001-2017, 5/17 associated with a supply pin group because of either (1) the current from the supply pin group (i.e., VDDIO) is required for the function of the electrical circuit(s) (I/O driver) that connect (high/low impedance) to that non-supply pin; or (2) a parasitic path exists between non-supply and supply pin group (e.g., open-drain type non-supply pin to a VCC supply pin group that connects to a nearby Nwell guard ring). associative memory: Synonym for "content-addressable memory". (Ref. IEC 748-2.) JESD100B.01, 12/02

ASSP: See "application-specific standard product".

| Terms, abbreviations, letter symbols, and definitions                                                                                                                                                                                     | References                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| asymmetry, full-scale (of a digital-to-analog converter with a bipolar analog range) ( $\Delta I_{FSS}$ or $\Delta V_{FSS}$ ): The difference between the absolute values of the two full-scale analog values.                            | JESD99C, 12/12                    |

| <b>asynchronous:</b> Describing operation in which the timing is not controlled by a clock.                                                                                                                                               | JESD230C, 11/16                   |

| NOTE For a NAND nonvolatile memory, asynchronous also means that data is latched with the WE_n signal for the write operation, and the RE_n signal for the read operation.                                                                |                                   |

| asynchronous circuit: A circuit whose changes of state are not controlled by a single clock.                                                                                                                                              | JESD12-1B, 8/93<br>JESD99C, 12/12 |

| ATE: Automated test equipment.                                                                                                                                                                                                            | JESD89A, 10/06                    |

| <b>attachment:</b> A capacitor, substrate cap, lid, heat sink, etc. that is glued, soldered, or mechanically affixed to a packaged device.                                                                                                | JESD22-B101C, 10/15               |

| <b>attribute data:</b> Data that result from counting items or classifying items into distinct nonoverlapping categories.                                                                                                                 | JESD557C, 4/15                    |

| NOTE Examples are count data (e.g., the number of nonconforming items), ordinal data (e.g., rank: first, second; classification: excellent, good, poor), nominal data (e.g., unordered groupings such as defect type), or pass/fail data. |                                   |

| <b>attribute memory select (RG):</b> An input that, when active (low), selects the attribute memory and, when inactive (high), selects the main memory for normal access.                                                                 | JESD21-C, 1/97#                   |

| NOTE Attribute memory is a separately accessed section of memory on the card and is generally used to record capacity and other configuration and attribute information. Main memory is used to store user data.                          |                                   |

| <b>audit:</b> The periodic review of procedures and observation of performed activities to evaluate compliance with requirements.                                                                                                         | JESD557C, 4/15                    |

|                                                                                                                                                                                                                                           |                                   |

<sup>#</sup> The definition in this referenced publication has been reworded in this dictionary for clarity or consistency.

| Те   | rms, abbreviations, letter symbols, and definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | References                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|      | horized aftermarket manufacturer: A manufacturer that meets one or more of the following eria.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | JESD243, 3/16                       |

| a)   | The aftermarket manufacturer is authorized by the <i>original component manufacturer</i> or intellectual property (IP) holder to produce and sell parts, usually due to an <i>original component manufacturer</i> or IP holder's decision to discontinue production of a part. Parts supplied are produced from material that has been                                                                                                                                                                                                                                                             |                                     |

|      | 1) transferred from the <i>original component manufacturer</i> or IP holder to the aftermarket manufacturer [usually in the form of die/wafer and test program(s)], or                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |

|      | 2) produced by the aftermarket manufacturer using <i>original component manufacturer</i> or IP holder tooling and/or intellectual property (IP).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     |

| b)   | The aftermarket manufacturer produces parts using semiconductor dice or wafers manufactured<br>by, and traceable to, an <i>original component manufacturer</i> or IP holder, that have been properly<br>stored until use and are subsequently assembled, tested, and qualified using processes that meet<br>the <i>original component manufacturer</i> or IP holder's technical specifications without violating<br>the <i>original component manufacturer</i> or IP holder's intellectual property rights (IPR) and are<br>authorized by the <i>original component manufacturer</i> or IP holder. |                                     |